- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

ချစ်ပ်ထုတ်လုပ်ခြင်းလုပ်ငန်းစဉ် (1/2)- wafer မှ ထုပ်ပိုးခြင်းနှင့် စမ်းသပ်ခြင်းအထိ ပြီးပြည့်စုံသော ရှင်းလင်းချက်

2024-09-18

တစ်ပိုင်းလျှပ်ကူးပစ္စည်း ထုတ်ကုန်တစ်ခုစီ၏ ထုတ်လုပ်မှုတွင် ရာနှင့်ချီသော လုပ်ငန်းစဉ်များ လိုအပ်ပြီး ထုတ်လုပ်မှု လုပ်ငန်းစဉ်တစ်ခုလုံးကို အဆင့်ရှစ်ဆင့်ဖြင့် ပိုင်းခြားထားသည်။wafer အပြောင်းအလဲနဲ့ - ဓာတ်တိုးခြင်း။ - ဓါတ်ပုံရိုက်နည်း - etching - ပါးလွှာသောရုပ်ရှင်အစစ်ခံ - အပြန်အလှန်ချိတ်ဆက်မှု - စမ်းသပ်ခြင်း - ထုပ်ပိုးမှု.

![]()

အဆင့် 1-Wafer လုပ်ဆောင်ခြင်း။

ဆီမီးကွန်ဒတ်တာ လုပ်ငန်းစဉ်အားလုံးသည် သဲတစ်ပွင့်ဖြင့် စတင်သည်။ အဘယ်ကြောင့်ဆိုသော် သဲထဲတွင်ပါရှိသော ဆီလီကွန်သည် wafers ထုတ်လုပ်ရန် လိုအပ်သော ကုန်ကြမ်းဖြစ်သည်။ Wafers များသည် ဆီလီကွန် (Si) သို့မဟုတ် gallium arsenide (GaAs) ဖြင့်ပြုလုပ်ထားသော ပုံဆောင်ခဲဆလင်ဒါတစ်ခုမှ ဖြတ်တောက်ထားသော အဝိုင်းအချပ်များဖြစ်သည်။ သန့်စင်မှုမြင့်မားသော ဆီလီကွန်ပစ္စည်းများကို ထုတ်ယူရန်အတွက် ဆီလီကာသဲ၊ ဆီလီကွန်ဒိုင်အောက်ဆိုဒ်ပါဝင်မှု 95% အထိရှိသော အထူးပစ္စည်းလိုအပ်ပြီး wafer ပြုလုပ်ရန် အဓိကကုန်ကြမ်းလည်းဖြစ်သည်။ Wafer processing သည် အထက်ဖော်ပြပါ wafer များပြုလုပ်ခြင်းလုပ်ငန်းစဉ်ဖြစ်သည်။

Ingot Cast

ပထမဦးစွာ၊ ၎င်းတွင်ရှိသော ကာဗွန်မိုနောက်ဆိုဒ်နှင့် ဆီလီကွန်များကို ခွဲခြားရန် သဲကို အပူပေးရန်လိုအပ်ပြီး အလွန်မြင့်မားသော သန့်စင်မှု အီလက်ထရွန်းနစ်အဆင့် ဆီလီကွန် (EG-Si) ရရှိသည်အထိ လုပ်ငန်းစဉ်ကို ထပ်ခါတလဲလဲ လုပ်ဆောင်သည်။ သန့်ရှင်းမြင့်မြတ်သော ဆီလီကွန်သည် အရည်အဖြစ်သို့ အရည်ပျော်သွားပြီး၊ ၎င်းသည် တစ်ပိုင်းလျှပ်ကူးပစ္စည်းထုတ်လုပ်ခြင်း၏ ပထမခြေလှမ်းဖြစ်သည့် "ingot" ဟုခေါ်သော တစ်ခုတည်းသော ပုံဆောင်ခဲအစိုင်အခဲပုံစံသို့ ခိုင်မာသွားပါသည်။

ဆီလီကွန်တိုင်များ (ဆီလီကွန်တိုင်များ) ၏ထုတ်လုပ်မှုတိကျမှုသည် အလွန်မြင့်မားပြီး နာနိုမီတာအဆင့်သို့ရောက်ရှိကာ တွင်ကျယ်စွာအသုံးပြုသည့်ကုန်ထုတ်လုပ်မှုနည်းလမ်းမှာ Czochralski နည်းလမ်းဖြစ်သည်။

အမြှေးဖြတ်ခြင်း။

ယခင်အဆင့် ပြီးပါက စိန်လွှဖြင့် အစွန်းနှစ်ချောင်းကို ဖြတ်တောက်ပြီး ထူထဲသော အတုံးလေးများဖြစ်အောင် လှီးဖြတ်ရပါမည်။ အချပ်၏အချင်းသည် wafer ၏အရွယ်အစားကိုဆုံးဖြတ်သည်။ ပိုကြီးပြီး ပိုပါးသော wafer များကို ပိုမိုအသုံးပြုနိုင်သော ယူနစ်များအဖြစ် ပိုင်းခြားနိုင်ပြီး ထုတ်လုပ်မှုကုန်ကျစရိတ်ကို လျှော့ချပေးပါသည်။ ဆီလီကွန် ingot ကို ဖြတ်တောက်ပြီးနောက်၊ နောက်ဆက်တွဲ အဆင့်များတွင် လုပ်ငန်းစဉ်အဖြစ် စံအဖြစ် သတ်မှတ်ရာတွင် အဆင်ပြေချောမွေ့စေရန် အချပ်များပေါ်တွင် "ပြားသော ဧရိယာ" သို့မဟုတ် "အံ" အမှတ်အသားများကို ပေါင်းထည့်ရန် လိုအပ်ပါသည်။

Wafer မျက်နှာပြင်ပေါ်လစ်တိုက်ခြင်း။

အထက်ပါ ဖြတ်တောက်ခြင်း လုပ်ငန်းစဉ်မှ ရရှိသော အချပ်များကို "bare wafers" ဟုခေါ်သည်၊ ဆိုလိုသည်မှာ မပြုပြင်ရသေးသော "အစိမ်း wafers" များဖြစ်သည်။ ဗလာ wafer ၏မျက်နှာပြင်သည် မညီမညာဖြစ်ပြီး ဆားကစ်ပုံစံကို ၎င်းပေါ်တွင် တိုက်ရိုက်ရိုက်နှိပ်၍မရပါ။ ထို့ကြောင့် ကြိတ်ခွဲခြင်းနှင့် ဓာတုဗေဒနည်းများဖြင့် မျက်နှာပြင်အညစ်အကြေးများကို ဦးစွာဖယ်ရှားရန်၊ ထို့နောက် ချောမွေ့သောမျက်နှာပြင်ဖြစ်လာစေရန် ပွတ်တိုက်ပြီး သန့်ရှင်းသော wafer မျက်နှာပြင်ရရှိရန် သန့်စင်ခြင်းဖြင့် ကျန်ရှိသော အညစ်အကြေးများကို ဖယ်ရှားရန် လိုအပ်ပါသည်။

အဆင့် 2: ဓာတ်တိုးခြင်း။

ဓာတ်တိုးခြင်းဖြစ်စဉ်၏ အခန်းကဏ္ဍမှာ wafer ၏ မျက်နှာပြင်ပေါ်တွင် အကာအကွယ်ရုပ်ရှင်တစ်ခု ဖန်တီးရန်ဖြစ်သည်။ ၎င်းသည် wafer ကိုဓာတုအညစ်အကြေးများမှကာကွယ်ပေးသည်၊ ပတ်လမ်းအတွင်းသို့ယိုစိမ့်သောလျှပ်စီးကြောင်းဝင်ရောက်ခြင်းမှကာကွယ်ပေးသည်၊ ion implantation လုပ်နေစဉ်အတွင်းပျံ့နှံ့မှုကိုတားဆီးကာ wafer သည် etching အတွင်းချော်ကျခြင်းမှကာကွယ်ပေးသည်။

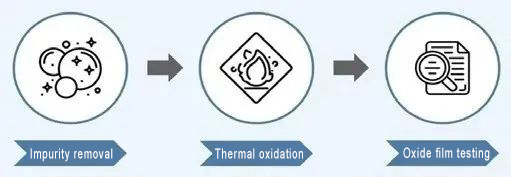

ဓာတ်တိုးခြင်းလုပ်ငန်းစဉ်၏ ပထမအဆင့်မှာ အညစ်အကြေးများနှင့် ညစ်ညမ်းမှုများကို ဖယ်ရှားရန်ဖြစ်သည်။ အော်ဂဲနစ်ဒြပ်စင်များ၊ သတ္တုအညစ်အကြေးများနှင့် ကျန်ရှိသောရေများကို အငွေ့ပျံရန် အဆင့်လေးဆင့် လိုအပ်သည်။ သန့်စင်ပြီးနောက် wafer ကို 800 မှ 1200 ဒီဂရီစင်တီဂရိတ်အထိ မြင့်မားသော အပူချိန်ပတ်ဝန်းကျင်တွင် ထားနိုင်ပြီး ဆီလီကွန်ဒိုင်အောက်ဆိုဒ် (ဆိုလိုသည်မှာ "အောက်ဆိုဒ်") အလွှာကို wafer ၏မျက်နှာပြင်ပေါ်ရှိ အောက်ဆီဂျင် သို့မဟုတ် ရေနွေးငွေ့စီးဆင်းမှုဖြင့် ဖွဲ့စည်းထားသည်။ အောက်ဆီဂျင်သည် အောက်ဆိုဒ်အလွှာမှတဆင့် ပျံ့နှံ့သွားပြီး အထူအမျိုးမျိုးရှိသော အောက်ဆိုဒ်အလွှာတစ်ခုအဖြစ် ဆီလီကွန်နှင့် ဓာတ်ပြုကာ ဓာတ်တိုးပြီးနောက် ၎င်း၏အထူကို တိုင်းတာနိုင်သည်။

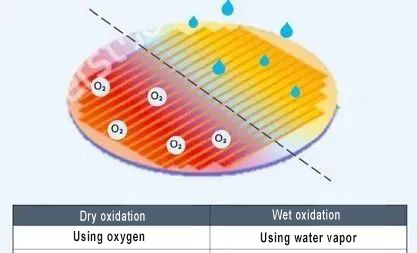

ဓာတ်တိုးခြင်း ခြောက်သွေ့ခြင်းနှင့် စိုစွတ်သော ဓာတ်တိုးခြင်း ဓာတ်တိုးခြင်း တုံ့ပြန်မှုတွင် မတူညီသော ဓာတ်တိုးဆန့်ကျင်ပစ္စည်းများအပေါ် မူတည်၍ အပူဓာတ်တိုးခြင်း လုပ်ငန်းစဉ်ကို ခြောက်သွေ့သော ဓာတ်တိုးခြင်းနှင့် စိုစွတ်သော ဓာတ်တိုးခြင်းဟူ၍ ခွဲခြားနိုင်သည်။ ယခင်က သန့်စင်သော အောက်ဆီဂျင်ကို အသုံးပြုပြီး ဆီလီကွန်ဒိုင်အောက်ဆိုဒ် အလွှာကို ထုတ်လုပ်ရန် နှေးကွေးသော်လည်း အောက်ဆိုဒ်သည် ပါးလွှာပြီး သိပ်သည်းသည်။ နောက်ပိုင်းတွင် အောက်ဆီဂျင်နှင့် အလွန်ပျော်ဝင်နိုင်သော ရေခိုးရေငွေ့ နှစ်ခုစလုံး လိုအပ်သည်၊ ၎င်းသည် ကြီးထွားမှုနှုန်း မြန်ဆန်သော်လည်း သိပ်သည်းဆနည်းသော အကာအကွယ်အလွှာသည် အတော်အတန်ထူသည်။

ဓာတ်တိုးဆန့်ကျင်ပစ္စည်းအပြင်၊ ဆီလီကွန်ဒိုင်အောက်ဆိုဒ်အလွှာ၏ အထူကို သက်ရောက်စေသည့် အခြားပြောင်းလဲမှုများ ရှိသေးသည်။ ပထမဦးစွာ wafer ဖွဲ့စည်းပုံ၊ ၎င်း၏ မျက်နှာပြင် ချို့ယွင်းချက်နှင့် အတွင်းပိုင်း မူးယစ်ဆေးဝါး သုံးစွဲမှုသည် အောက်ဆိုဒ် အလွှာ ထုတ်လုပ်မှု နှုန်းအပေါ် သက်ရောက်မှု ရှိမည်ဖြစ်သည်။ ထို့အပြင် ဓာတ်တိုးပစ္စည်းမှ ထုတ်ပေးသော ဖိအားနှင့် အပူချိန် မြင့်မားလေ၊ အောက်ဆိုဒ်အလွှာကို ပိုမိုမြန်ဆန်စွာ ထုတ်ပေးနိုင်မည်ဖြစ်သည်။ ဓာတ်တိုးခြင်းလုပ်ငန်းစဉ်တွင်၊ wafer ကိုကာကွယ်ရန်နှင့် oxidation degree ကွာခြားမှုကိုလျှော့ချရန်အတွက်ယူနစ်ရှိ wafer ၏အနေအထားအရ dummy sheet ကိုအသုံးပြုရန်လိုအပ်သည်။

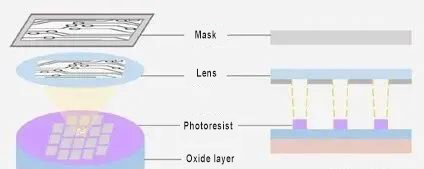

အဆင့် 3- ဓါတ်ပုံရိုက်နည်း

Photolithography သည် အလင်းမှတဆင့် wafer ပေါ်သို့ ဆားကစ်ပုံစံကို "ပုံနှိပ်ခြင်း" ဖြစ်သည်။ wafer ၏မျက်နှာပြင်ပေါ်တွင် ဆီမီးကွန်ဒတ်တာထုတ်လုပ်ခြင်းအတွက် လိုအပ်သော လေယာဉ်မြေပုံကိုဆွဲခြင်းဖြင့် ၎င်းကိုနားလည်နိုင်သည်။ ဆားကစ်ပုံစံ၏ ကောင်းမွန်မှု မြင့်မားလေ၊ အဆင့်မြင့် photolithography နည်းပညာဖြင့် ရရှိရမည့် အချောထည် ချစ်ပ်များ၏ ပေါင်းစပ်မှု မြင့်မားလေဖြစ်သည်။ အထူးသဖြင့်၊ photolithography ကို အဆင့်သုံးဆင့် ခွဲခြားနိုင်သည်- coating photoresist၊ exposure နှင့် development။

အပေါ်ယံပိုင်း

wafer ပေါ်တွင် ဆားကစ်တစ်ခုဆွဲခြင်း၏ ပထမအဆင့်မှာ အောက်ဆိုဒ်အလွှာပေါ်တွင် photoresist ကို ဖုံးအုပ်ရန်ဖြစ်သည်။ Photoresist သည် ၎င်း၏ဓာတုဂုဏ်သတ္တိများကို ပြောင်းလဲခြင်းဖြင့် wafer ကို "ဓာတ်ပုံစက္ကူ" ဖြစ်စေသည်။ wafer ၏မျက်နှာပြင်ပေါ်ရှိ photoresist အလွှာပိုပါးလေ၊ အပေါ်ယံညီညွှတ်လေလေ၊ နှင့်ရိုက်နှိပ်နိုင်သောပုံစံပိုကောင်းလေဖြစ်သည်။ ဤအဆင့်ကို "spin coating" နည်းလမ်းဖြင့် လုပ်ဆောင်နိုင်သည်။ အလင်း (ခရမ်းလွန်ရောင်ခြည်) ဓာတ်ပြုမှု ကွာခြားချက်အရ ဖိုထရစ္စစစ်ကို အပေါင်းနှင့် အနုတ်ဟူ၍ နှစ်မျိုး ခွဲခြားနိုင်သည်။ အလင်းနှင့်ထိတွေ့ပြီးနောက် ပြိုကွဲပြီး ပျောက်ကွယ်သွားကာ အလင်းမရရှိသော ဧရိယာပုံစံကို ချန်ထားကာ နောက်တစ်ခုသည် အလင်းရောင်နှင့်ထိတွေ့ပြီးနောက် ပေါ်လီမာဆန်ပြီး ထိတွေ့ထားသောအစိတ်အပိုင်း၏ပုံစံအတိုင်း ပေါ်လာမည်ဖြစ်သည်။

ထိတွေ့ခြင်း

wafer ပေါ်တွင် photoresist ဖလင်ကို ဖုံးအုပ်ပြီးနောက်၊ အလင်းထိတွေ့မှုကို ထိန်းချုပ်ခြင်းဖြင့် ဆားကစ်ပုံနှိပ်ခြင်းကို အပြီးသတ်နိုင်သည်။ ဤဖြစ်စဉ်ကို "ထိတွေ့မှု" ဟုခေါ်သည်။ အလင်းဝင်သည့်ကိရိယာများမှတစ်ဆင့် ကျွန်ုပ်တို့သည် အလင်းကိုရွေးချယ်နိုင်သည်။ အလင်းသည် ဆားကစ်ပုံစံပါရှိသော မျက်နှာဖုံးကို ဖြတ်သွားသောအခါ၊ ဆားကစ်ကို အောက်ပါ photoresist ဖလင်ဖြင့် ဖုံးအုပ်ထားသော wafer ပေါ်တွင် ရိုက်နှိပ်နိုင်သည်။

ထိတွေ့မှုလုပ်ငန်းစဉ်အတွင်း၊ ပုံနှိပ်ပုံစံပိုကောင်းလေ၊ နောက်ဆုံးချစ်ပ်၏ အစိတ်အပိုင်းများ ပိုမိုထားရှိနိုင်လေဖြစ်ပြီး ထုတ်လုပ်မှုစွမ်းဆောင်ရည်ကို မြှင့်တင်ရန်နှင့် အစိတ်အပိုင်းတစ်ခုစီ၏ ကုန်ကျစရိတ်ကို လျှော့ချရန် ကူညီပေးသည်။ ဤနယ်ပယ်တွင်၊ လက်ရှိအာရုံစူးစိုက်မှုကို ဆွဲဆောင်နိုင်သော နည်းပညာအသစ်မှာ EUV lithography ဖြစ်သည်။ Lam Research Group သည် မဟာဗျူဟာလုပ်ဖော်ကိုင်ဖက် ASML နှင့် imec တို့နှင့်အတူ ခြောက်သွေ့သော ဖလင်ဓါတ်ခံနည်းပညာအသစ်ကို ပူးတွဲတီထွင်ခဲ့သည်။ ဤနည်းပညာသည် EUV lithography exposure လုပ်ငန်းစဉ်၏ ကုန်ထုတ်စွမ်းအားနှင့် အထွက်နှုန်းကို ကြည်လင်ပြတ်သားစွာ မြှင့်တင်ပေးခြင်းဖြင့် (အကောင်းမွန်ဆုံး circuit width အတွက် အဓိကအချက်) ကို တိုးတက်စေနိုင်သည်။

ဖွံ့ဖြိုးတိုးတက်ရေး

ထိတွေ့ပြီးနောက်အဆင့်မှာ developer ကို wafer ပေါ်တွင်ဖြန်းရန်ဖြစ်ပြီး ရည်ရွယ်ချက်မှာ ပုံစံ၏မဖုံးထားသောဧရိယာရှိ photoresist ကိုဖယ်ရှားရန်ဖြစ်ပြီး ပုံနှိပ်ဆားကစ်ပုံစံကိုထုတ်ဖော်နိုင်စေရန်ဖြစ်သည်။ တီထွင်မှုပြီးမြောက်ပြီးနောက်၊ circuit diagram ၏အရည်အသွေးကိုသေချာစေရန်အတွက် အမျိုးမျိုးသော ကိရိယာများနှင့် optical microscopes များဖြင့် စစ်ဆေးရန် လိုအပ်ပါသည်။

အဆင့် 4: အလှဆင်ခြင်း။

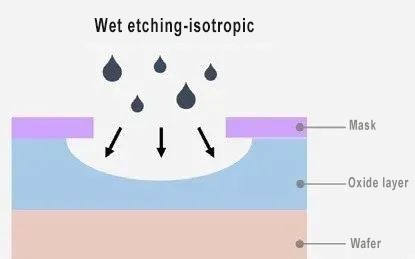

wafer ပေါ်တွင် circuit diagram ၏ photolithography ကိုပြီးစီးပြီးနောက်၊ ပိုလျှံနေသော အောက်ဆိုဒ်ဖလင်များကို ဖယ်ရှားရန်နှင့် semiconductor circuit diagram ကိုသာချန်ထားရန် etching process ကိုအသုံးပြုပါသည်။ ထိုသို့ပြုလုပ်ရန်၊ ရွေးချယ်ထားသော ပိုလျှံနေသော အစိတ်အပိုင်းများကို ဖယ်ရှားရန်အတွက် အရည်၊ ဓာတ်ငွေ့ သို့မဟုတ် ပလာစမာကို အသုံးပြုသည်။ အသုံးပြုထားသော အရာများပေါ် မူတည်၍ သတ္တုစပ်ခြင်းအတွက် အဓိက နည်းလမ်း နှစ်ခု ရှိသည်- အောက်ဆိုဒ် ဖလင်ကို ဖယ်ရှားရန် ဓာတုဗေဒနည်းဖြင့် တုံ့ပြန်ရန် ဓာတုဗေဒနည်းဖြင့် တုံ့ပြန်ရန်အတွက် စိုစွတ်သော ခြစ်ခြင်း နှင့် ဓာတ်ငွေ့ သို့မဟုတ် ပလာစမာကို အသုံးပြု၍ အခြောက်လှန်ခြင်း စသည်တို့ ဖြစ်သည်။

စိုစွတ်သော etching

အောက်ဆိုဒ်ရုပ်ရှင်များကို ဖယ်ရှားရန် ဓာတုဗေဒဖြေရှင်းချက်များကို အသုံးပြု၍ စိုစွတ်သော ထွင်းထုခြင်းသည် ကုန်ကျစရိတ် သက်သာခြင်း၊ ခြစ်ထုတ်ခြင်း မြန်ဆန်ခြင်းနှင့် ကုန်ထုတ်စွမ်းအား မြင့်မားခြင်း၏ အားသာချက်များဖြစ်သည်။ သို့သော်၊ စိုစွတ်သော etching သည် isotropic ဖြစ်သည်၊ ဆိုလိုသည်မှာ ၎င်း၏အမြန်နှုန်းသည် မည်သည့် ဦးတည်ရာတွင်မဆို အတူတူပင်ဖြစ်သည်။ ၎င်းသည် မျက်နှာဖုံး (သို့မဟုတ် ထိလွယ်ရှလွယ် ဖလင်) ကို ထွင်းထုထားသည့် အောက်ဆိုဒ်ဖလင်နှင့် လုံးလုံးလျားလျား လိုက်လျောညီထွေမဖြစ်စေသောကြောင့် အလွန်ကောင်းမွန်သော ဆားကစ်ပုံများကို လုပ်ဆောင်ရန် ခက်ခဲသည်။

အခြောက်ခံခြင်း

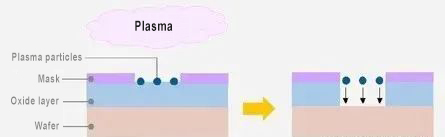

Dry etching ကို အမျိုးအစားသုံးမျိုး ခွဲခြားနိုင်ပါတယ်။ ပထမအချက်မှာ etching gases (အဓိကအားဖြင့် ဟိုက်ဒရိုဂျင် ဖလိုရိုက်) ကို အသုံးပြုသည့် ဓာတု etching ဖြစ်သည်။ စိုစွတ်သော etching ကဲ့သို့ပင်၊ ဤနည်းလမ်းသည် isotropic ဖြစ်ပြီး၊ ဆိုလိုသည်မှာ ၎င်းသည် ကောင်းမွန်သော etching အတွက် မသင့်တော်ပါ။

ဒုတိယနည်းလမ်းမှာ ပလာစမာရှိ အိုင်းယွန်းအိုင်းယွန်းကို အသုံးပြု၍ ပိုလျှံနေသော အောက်ဆိုဒ်အလွှာကို ရိုက်ခတ်ခြင်းနှင့် ဖယ်ရှားခြင်းအား ရုပ်ပိုင်းဆိုင်ရာ sputtering ပြုလုပ်ခြင်းဖြစ်သည်။ anisotropic etching method တစ်ခုအနေဖြင့်၊ sputtering etching သည် အလျားလိုက်နှင့် ဒေါင်လိုက် လမ်းကြောင်းများတွင် အမျိုးမျိုးသော etching rate ရှိသည်၊ ထို့ကြောင့် ၎င်း၏ fineness သည် chemical etching ထက် ပိုမိုကောင်းမွန်ပါသည်။ သို့သော် ဤနည်းလမ်း၏ အားနည်းချက်မှာ အိုင်းယွန်းတိုက်မှုကြောင့် ဖြစ်ပေါ်လာသော ရုပ်ပိုင်းဆိုင်ရာ တုံ့ပြန်မှုအပေါ် လုံးလုံးလျားလျား မှီခိုနေသောကြောင့် etching speed နှေးကွေးခြင်း ဖြစ်သည်။

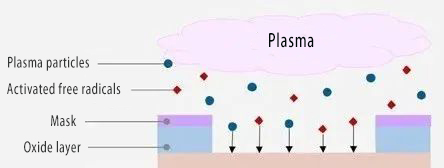

နောက်ဆုံး တတိယနည်းလမ်းမှာ ဓာတ်ပြုအိုင်းယွန်း etching (RIE) ဖြစ်သည်။ RIE သည် ပလာစမာကို အိုင်ယွန်ဇေးရှင်းရုပ်ပိုင်းဆိုင်ရာ etching အတွက် ပလာစမာကိုအသုံးပြုနေစဉ်တွင် ပလာစမာအသက်သွင်းပြီးနောက် ထွက်လာသည့် free radicals များ၏အကူအညီဖြင့် RIE သည် ပထမနည်းလမ်းနှစ်ခုကို ပေါင်းစပ်ထားသည်။ ပထမနည်းလမ်းနှစ်ခုထက်ကျော်လွန်သော etching speed အပြင်၊ RIE သည် တိကျမှုမြင့်မားသောပုံစံ etching ကိုရရှိရန် အိုင်းယွန်း၏ anisotropic လက္ခဏာများကို အသုံးပြုနိုင်သည်။

ယနေ့ခေတ်တွင်၊ ကောင်းမွန်သော semiconductor circuit များ၏ အထွက်နှုန်းကို တိုးတက်စေရန် ခြောက်သွေ့သော etching ကို တွင်တွင်ကျယ်ကျယ် အသုံးပြုလာပါသည်။ full-wafer etching တူညီမှုကို ထိန်းသိမ်းရန်နှင့် etching speed တိုးလာရန် အရေးကြီးပြီး ယနေ့ခေတ် အဆင့်မြင့်ဆုံး dry etching equipment သည် စွမ်းဆောင်ရည်မြင့်သော အဆင့်မြင့် logic နှင့် memory chips များ ထုတ်လုပ်မှုကို ပံ့ပိုးပေးပါသည်။

VeTek Semiconductor သည် ပရော်ဖက်ရှင်နယ် တရုတ်ထုတ်လုပ်သူဖြစ်သည်။Tantalum Carbide အပေါ်ယံပိုင်း, ဆီလီကွန်ကာဗိုက်အလွှာ, အထူးဂရပ်ဖစ်, ဆီလီကွန်ကာဗိုက် ကြွေထည်များနှင့်အခြား Semiconductor ကြွေထည်များ. VeTek Semiconductor သည် ဆီမီးကွန်ဒတ်တာစက်မှုလုပ်ငန်းအတွက် အမျိုးမျိုးသော SiC Wafer ထုတ်ကုန်များအတွက် အဆင့်မြင့်ဖြေရှင်းချက်များအား ပံ့ပိုးပေးရန် ကတိပြုပါသည်။

အထက်ဖော်ပြပါ ထုတ်ကုန်များကို စိတ်ဝင်စားပါက ကျွန်ုပ်တို့ထံ တိုက်ရိုက်ဆက်သွယ်နိုင်ပါသည်။

Mob: +86-180 6922 0752

WhatsAPP: +86 180 6922 0752

အီးမေးလ်- anny@veteksemi.com